① 강의를 통해 배운 내용을 정리해주세요! (200자 이상)

PART1

기초적인 반도체 개념과 소자에 대해서 배워볼 것이다.

소위 반도체 8대 공정 포토 공정에서 세정 공정까지 양품과 불량품을 선별하는 EDS 조립공정인 패키지 공정까지 커버하겠다.

통상 전기전도도에 의해서 정의를 한다.

전기가 얼마나 잘 흐르는지에 대한것이 전기 전도도이다.

저항은 물질에 따라서 고유한 값을 가진다.

반도체는 도체와 부도체 중간이라고 생각하면 된다.

Si,Ge의 단원소 반도체가 있고

화합물 반도체에는 GaAs가 존재한다.

구리의 비저항은 1.66x10^-6 옴 정도 되는데

반도체가 유리한 이유는 도핑을 통해서

원하는 전도도 혹은 비저항 값을 맞출 수 있다.

즉 가변적이다.

전하

전하에 대해서 알아보도록 하자

전기를 흐르게 하는것이 무엇인가?

전하는 양성과 음성의 극성의 전기를 띈 입자라고 생각하면 된다

단위는 C [Coulomb]

단위 시간 당 이동한 전하량(C/se)=>전류[A]

극성을 띈 입자들이 움직이면 그것이 전류가 흐르는것 이다.

캐리어

캐리어는 전하를 이동시켜 전류를 발생시키는 전하 운송자이다.

두가지가 존재하는데 전자와 정공이 존재한다.

정공은 양전하 음전하는 전자를 의미한다.

전자가 이동하면 전자가 있던자리가 비어있게 되고

빈공간에 구멍이 생기는데 정공은 전자가 이동하는 방향의

반대 방향으로 움직인다고 생각할 수 있는데 이것을 정공이라고 명명한다.

정공은 -방향으로 이동하고

전자는 +방향으로 이동한다.

정전 용량(Capacitor)

전기가 통하는 도체 전극 사이에 절연체가 존재하는 구조이다.

양단에 +-전압을 가하게 되면 양단에 +charge와 -charge가 모이게 된다.

서로 +-이기 때문에 인력이 존재하고 외부의 전압을 제거 하더라도

일정 시간동안 charge가 남아있게 된다==> 충전의 원리다.

일정시간동안 전하가 보존된다.

실리콘을 사용하는 이유는 다양하다.

싸고 특성이 좋고 녹는점이 높아서 프리하고

노하우가 쌓인 이유도 한몫한다.

원자번호가 14번으로 4족 원소이다.

원자 간 공유결합을 이루고 있고

0K 에서는 에너지가 없기 때문에 실리콘이

원자핵에 묶여서 구속전자로 묶여있다.

0K 이상에서는 전자-정공 쌍(EHP 생성)이 생성된다.

순수한 반도체에서는 항상 전자와 정공의 농도가 같아야 한다.

불순물이 두가지가 있는데

5족 원소와 3족 원소가 존재한다.

불순물의 농도를 조절하므로서 고 농도 n+와 저농도 n-로 만들 수 있다.

5족원소를 주입하면 N형 반도체가 된다.

다수캐리어는 전자가 되고

정공은 소수캐리어가 되는데

열적 생성이다.

P형 반도체는 반대로 다수캐리어가 정공이고

소수 캐리어는 전자가 된다.

이 전자는 자유전자로서 열적으로 생성된 전자다.

P형 반도체에 +전압을 가하고

N형 반도체에 -전압을 가하면

forward 바이어스를 가하게 된다.

홀과 전자가 접합면을 사이에 두고 서로 크로스를 하고 순방향으로 흐르게 된다.

반대로 역방향 전압을 가해주면

캐리어들이 접합면의 반대로 가고

전류가 흐르지 않는 상태가 된다.

교류파형을 집어 넣어주면 -쪽 신호는 전류가 흐르지 않아서 커트 되는

정류작용이 일어나고 그래서 정류기로 사용할 수 있다.

MOSFET

전계효과=>정전용량의 원리

P형 기판에 n타입 반도체가 들어가고

소스 드레인

구조는 p형 실리콘을 적절하게 도핑해서

전도성을 띄게 하고 p타입기판과 금속 전극사이에 절연체(산화막)를 두게 된다.

이렇게 해서 MOS 캐패시터 구조가 형성되는 것 이다.

반대로 N형 기판에 p형 반도체를 소스 드레인으로 하는

MOSFET을 pMOS로 한다.

소스와 드레인에서는 다수 캐리어가 전자

기판은 정공이 다수캐리어가 된다.

이때 게이트에 +전압을 걸고

게이트에는 +차지

반대편 전극에는 -차지가 유도가 된다.

원래 p형 반도체였다가

n형 반도체로 바뀌게 되고

드레인에 있던 전자가 소스로 빠져나가게 된다.

문턱 전압 이상이 되면 채널이 형성되어서

전류가 흐르는 것이다.

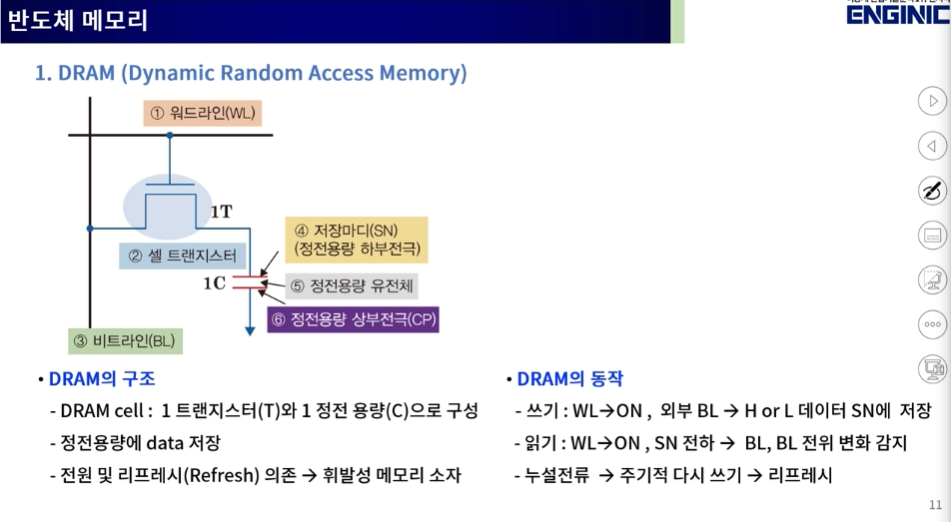

DRAM은 기본적으로

트랜지스터하나와 커패시터 하나로 이루어진다.

전자가 포진되면 일정시간 보존되는 원리를 이용한다.

비트라인을 통해서 왔다 갔다 하는데

트랜지스터가 ON이 되면 트랜지스터를 통해서

캐패시터 안에 전하가 충전되면 WRITE

반대로 트랜지스터가 ON 된 상태에서 비트라인에 실려서

나가게 되면 READ 동작이다.

DRAM은 여러가지 경로를 통해서 빠져 나갑니다. 시간을 통해서

그래서 주기적으로 다시 써줘야하는데

이것을 리프레시라고 부른다.

==>전원이 꺼지면 사라지게 되는 휘발성 메모리이다.

비휘발성 메모리인 낸드 플래시를 살펴보자

층간절연막과 하나의 게이트가 더 추가 된다.

제어게이트는 셀을 선택하는 워드라인이고

부유게이트는 전자를 넣거나 빼서 데이터를 저장한다.

터널 산화막은 전하가 터널링하는 산화막이다.

고전계에서는 전자가 통과하지만

저전계에서는 전자가 이탈하는것을 방지하는 절연물체로서 동작한다.

쓰기동작에는 프로그래밍과 소거 동작이 있다.

전자들이 산화막을 뚫고 부유게이트로 들어가게 되고

이것이 프로그래밍 동작이며

부유게이트에서 전자가 빠져나오게 되면 소거 동작이다.

읽기 동작은 부유게이트의 전자 유무에 따라서 문턱 전압 변동을 감지하는것이다.

PART2

SRAM DRAM NAND Flash를 알아볼것이다.

SRAM은 CPU가 가장 자주 사용하는 데이터를 저장한다.

SRAM은 CPU에 내장(임베디드)되어 있는 메모리이다.

트랜지스 동작만 하기 때문에 속도가 제일 빠르다.

하지만 단위 셀 면적이 굉장히 커서 단가가 높은 단점이 있고

휘발성 메모리에서 데이터가 저장될때는 전원이 공급이 되어있어야 한다.

DRAM

디램은 주램으로서 밑에 있는 낸드 플래시등의 메모리와

S램 사이에서 중계자 역할을 하며

SRAM과 낸드 플래시 사이의 위치다.

휘발성 메모리이다.

낸드 플래시

스토리지 메모리 역할을 하는데

단위 셀 면적이 적어서 고 용량으로서 단가가 낮으나

속도가 느리지만 비 휘발 성 메모리가 된다.

클라우드 스토리지

인터넷 기반의 스토리지이다.

속도가 느리고 보안에 취약하지만 비 휘발성 메모리이다.

SRAM 셀은 6개의 트랜지스터로 구성이 되어있어서

셀 면적이 크고 고속 동작이 가능 합니다.

두 개의 CMOS 인버터가 서로 교차로 결합한다.

인버터에 대해서 잠시 집고 넘어 가자

인풋에 0을 넣으면 1이되고

1을 넣으면 0이 된다.

서로 물고 물리는 교차 결합이기 때문에

VDD와 VSS가 계속 인가 되는 상황에서는 전혀 바뀌지 않는다.

P트랜지스터 2개

N트랜지스터 두개

두개의 access 트랜지스터로 구성이 된다.

워드 라인은 게이트 역할을 한다.

양쪽의 비트라인과 빗/ 라인이 존재하며

상보적 데이터 형태로 저장된다.

static은 전원이 공급하는 동안은 데이터 보존이 되며

전원이 꺼지면 휘발성임을 의미한다.

RAM은 x와 y 주소 지정이 되면 어디서든 임의로 접근이 가능하다는 의미다.

좌표를 지정하면 해당 셀로 접근이 가능하다는 의미다.

대기 상태가 되면

워드라인은 OFF 상태가 되어서

비트라인과 래치 트랜지스터가 서로 격리되어있다.

대기 상태에서는 비트라인이 1로 예비로 충전되어있다=>외부에서 전압이 가해지고 있다.

추후에 0이나 1이 써져 있으면 어떻게 보존 될까?

Q가 0이면 오른쪽 인버터에 0으로 입력이 들어가고

인버터출력으로 1이 출력된다. 그래서 P2가 ON이 되고

N3는 OFF가 되니까 VDD가 충전이 되면서 Q/가 1로 나온다

반대로 P1이 OFF가 되고 차지가 N1(ON)으로 빠지게 되어

차지가 계속 0으로 유지된다.

즉 전원이 공급되는 동안에는 0과 1이 유지된다!

쓰기 동작에 대해서 알아보자

래치되어있는 이전상태와 반대 데이터를 쓰는 경우 두가지로 나눌 수 있다.

대기상태에서는 프리차지가 되어 있는데

WL이 ON이 되어서

N2와 N4가 ON 상태가 된다.

프리차지 되어있던 데이터는 끊기게 되고

외부에서 0과 1을 강제적으로 집어 넣어주는데

원래 써져 있던 데이터와 동일해서 아무 문제 없다.

이전상태와 반대 데이터를 사용하게 되면 어떻게 될까?

1과 0 데이터를 들어오게 한다.

N2가 ON 되어있어서 1이 빠져 나가게 되고

VDD 차지가 /BL로 빠져 나가게 된다.

즉, 방전 되게 된다.

/Q가 N4를 통해서 방전 된다.

1->0상태가 된다.

방전되던 차지들이 바뀌게 된다.

/Q는 바로 0으로 떨어지는데

Q는 0으로 떨어진 상태에서 변하기 때문에

딜레이가 존재해서

해석하는데 주의가 필요하다.

차지가 변화가

P2의 정전 용량이 크지만

N4의 용량이 작으면

방전이 느리게 될 수 있기 때문에

N4가 P2의 구동 능력보다 좋아야 한다.(물이 빠지는 원리와 동일)

읽는 동작에 대해서 알아보자

대기 상태에서는 비트라인이 항상 프리차지 되어 있다.

이전 상태ㅇ가 0과 1이기 때문에

P2와 N1이 ON 되어있다.

읽기 모드에 들어가면 WL이 ON 된다.

프리차지되어있던게 끊겨서

플로팅 상태가 된다.

외부에서 인가되있던 전압이 끊긴다.

전원을 공급을 안하면 확 떨어져 버리지는 않는다

왜냐하면 의도치 않는 기생 커패시터들이 존재하고

일정기간동안 유지되는 플로팅 상태가 된다.

주변 환경에 따라서 두 라인의 전압 수준이 바뀌게 된다.

N2 쪽을 보면 N2와 N4는 ON이 되고

이전 상태가 N1이 ON 상태고

N2와 N1을 통해서 빠져 나가면서 비트라인은 0볼트로 내려가게 된다.

반대 /BL은 1로 가게 된다.

비트라인을 감지해서 외부로 빼내게 된다.

N2와 N1의 관계를 알아야 되는데

아까와 같이 N1의 구동 능력이 좋아야 방전이 빠르게 일어난다.

같은 이유로 N3의 구동 능력이 좋아야 하고

N2와 N4가 좋아야 하며

PMOS가 순이면 에러 확률이 제일 적다.

PART3

DRAM 셀의 동작 원리를 공부하도록 하겠습니다.

하나의 nMOS와 TR 하나로 구성되어있다.

커패시터에 데이터를 저장하는데 시간이 지나면

누설전류에 의해서 데이터가 사라지기 때문에 리프레시 해줘야 한다.

SRAM과 달리 주기적으로 다시 써줘야한다=>DYNAMIC

또한 휘발성 메모리 소자이다.

비트라인은 소스나 드레인 쪽에 접근해 있다.

쓰기나 읽기 등 외부에서 셀로 혹은

셀이나 외부로 데이터가 이동되는 통로다.

워드라인은 셀커패시터를 연결하거나 끊는 스위치 역할을 하는

게이트 역할을 한다.

커패시터는 두개의 전극이 필요하다.

그 사이에는 유전체가 들어있다.

하부 전극은 스토리지 노드로 표현하고

SN으로 명명하고 상부 전극은 CP라고 정의를 한다.

하부 전극에 1이 걸리면 충전된다고 하고

0이 되면 방전되는것이다.

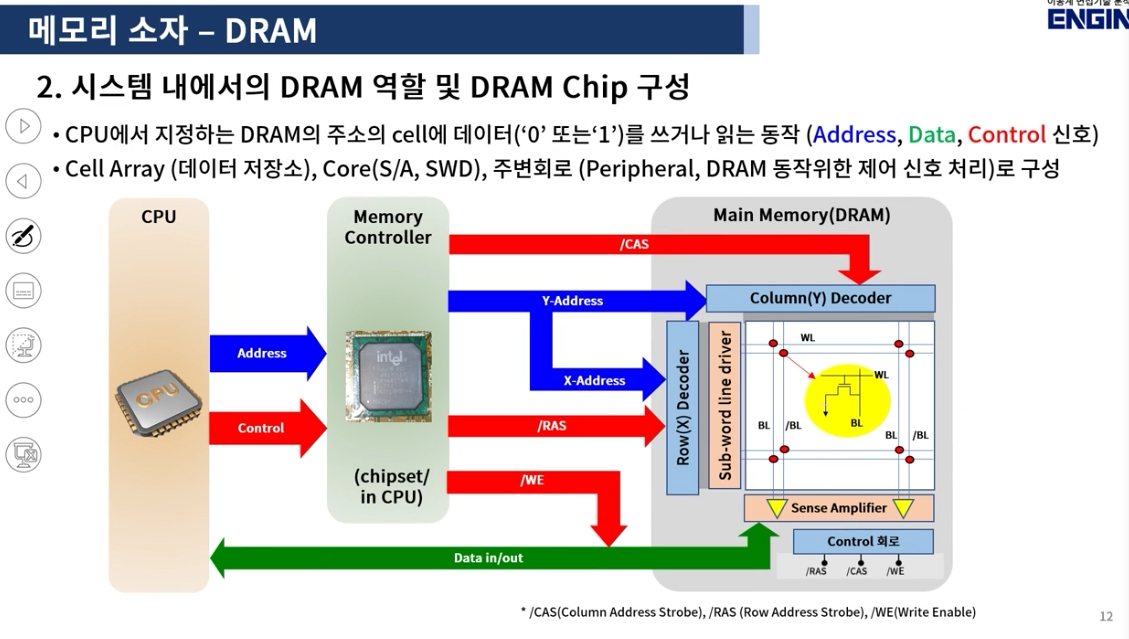

DRAM 셀의 동작을 알기 위해서 큰 그림을 보자

시스템이라고 하는것은 PC라고 생각하면 된다.

가장 중요한 장치는 CPU다. CPU가 하는 일은 주로 연산하고

판단을 하거나 제어를 하는 사람으로 따지면 두뇌와 같은 역할을 한다.

CPU 동작을 위해서는 데이터가 필요하다.

데이터가 필요한데 데이터는 누가 가지고 있느냐?

모든 프로세스 할 때 주 메모리인 DRAM에 들어가 있다.

CPU와 DRAM은 긴밀하게 상호작용하며 CPU가 명령을 한다.

명령이 세가지 인데

1.Adress

2.Data

3.Control

명령어 셋을 준다.

CPU와 DRAM이 서로 상호 작용하게 된다.

데이터는 CPU와 DRAM이 다이렉트로 주고 받는다.

DRAM과 커뮤니케이션 하는것이 아니라

메모리 컨트롤러라고 하는 중간 매개체를 통해서 컨트롤 한다.

요즘은 CPU안에 칩셋을 내장하는 형태가 많다.

워드라인과 비트 라인이 서로 교차하는 지점에서 만들어 지는것이

DRAM의 셀이 된다. DRAM 셀로 어레이 되있는것을

CELL ARRAY라고 부른다.(저장소)

워드 라인에 전압을 인가해주는것을 서브 워드 라인 드라이버

비트라인과 비트바이 라인의 전압 차이를 비교해서 증폭 시키는

Sense Amplifer

이것을 합쳐서 CORE라고 표현한다.(셀의 XY를 컨트롤)

Comlumn Decoder, Row Decoder,Control등이 주변회로라고 부른다.

메모리 컨트롤러가 어느 어드레스를 주었을 때

CAS라는 신호(Y어드레스)

RAS라는 신호(X어드레스)

Write Enable 신호가 들어오면 쓰기

없으면 리딩 동작을 한다.

CAS RAS WE가 BUS를 통해서 명령어를 주고 받는다.

대기 상태는 가만히 있는것이다. 동작을 하지 않는것인데

DRAM 특유의 리프레시 등 Stand-by 상태다.

WL은 OFF 되어 있다.

SN,BL이 격리 되어있다.

WL이 오프 되어 있어서

SLAM에서도 비트라인과 비트바이 라인이 프리차지 되어 있는데하이데이터(1)의 1/2이 인가가 되어있다. 비트라인과 비트라인 바가 S/A로 연결되어있다.대기 상태일때는 Vcore/2로 프리 차지 되어있다.

수조모델을 통해서 쉽게 알아보도록 하자.

커패스터를 표현하면 들어있는 물의 높이를 전압이라고 표현했을 때 Q=CV 물의 총량 이것을 전하량이라고 표현한다.

커패시터는 우리가 원하는 의도적으로 만들어준 커패시터인데

우리가 원하지 않는 기생 커패시터가 존재한다.기생 커패시터가 무엇인가?BL와 /BL이 존재하는데

비트라인과 워드라인 사이에 보면 녹색으로 되어있는것이 비트라인인데 트렌지스터 게이트가 있고 정션과 연결이 되어있는데비트라인과 워드라인 사이에 기생 커패시턴스가 존재한다.

디플리션에 의한 커패시터도 존재를 한다.

커패시터라고 하는것은 전극 두개에 유전체

원치 않는 기생 커패시터들이 많이 생긴다.

Cs가 0이라고 했을 때 비트라인과 비트라인 바는 Vcore/2로 공급 중이고 이것이 대기 상태이다.

대기 상태를 보면 타겟으로 하는 셀에 아무것도 없는 0 상태 이다.WL이 오프 상태로 되어있다.

물은 Vcore/2로 대기 중이다.

WE 신호가 들어가게 되면 오프 되어있던 게이트가 0이 된다.

이 때 프리 차지 되어있던 Vcore/2

왼쪽에는 Vcore 레벨로 공급하고 CB와 Cs로 똑같은 레벨로 차게 되고

비트라인과 비트 바이 라인에 차이가 생긴다.

쓰기 상태가 끝나면 1로 채워지고 벨브를 잠궈 버리고

다시 대기 상태가 되면 Vcore/2로 채워지게 된다.

하이데이터가 들어와 있었는데 워드라인이 뜨게 되면

전하가 빠져 나가고

비교 후에 증폭해서 외부로 빼내는것이 읽기 동작이다.

셀 캐패시터에는 1이 채워지고 있고

프리차지 되어있고

읽기 동작 명령을 내리면 charge sharing을 시키고

읽기 동작에서 WL이 ON 되고 VBL 공급이 중단되서

플로팅 상태가 된다. 워드 라인이 열렸기 때문에 물이 비트라인 쪽으로 흘러가고수위가 내려가게 된다. 비트라인까지의 수위까지 수위가 내려가게 되서조금 올라가게 되는데 델타 VBL이라고 부른다.이것을 전하 공유라고 부른다.==> '파괴적 읽기'라고 부르는데

걱정하지 않아도 되는이유는 S/A에서 증폭을 시켜주기 때문이다.오른쪽보다 왼쪽이 올라가있기 때문에 차이를 벌린다. ==>스위치가 열려있어서 다시 수위가 올라간다.==>대기 상태가 되면 WL이 OFF 되어서 다시 1로 유지되서유지된다.

PART4

전기적으로 정리해보자.Cb와 Cs가 있는데 Cb는 기생 캡토탈 차지량은 Q=CV로 계산할 수 있다.

전하 공유에 의한 차지 갑은 V'BL 값을 대입해서 구할 수 있다.델타 Vbl을 증가 시키면 안정적인 동작이 가능하기 때문에Cs은 높이고 Cb값을 낮춰야한다.

프리 차지하는 동안에 Vcore/2로 프리차지 되어있다.Vpp는 WL에 높은 전압이 가해지는데프리차지가 부유 상태로 되게 되고 비트라인 쪽의 전압이 조금 커지게 되고 S/A가 감지해서 증폭시킨다.

그 후에 CSL 통로를 통해서 I/O로 빠져 나간다.

Cs를 어떻게 늘릴것인가?유전체의 유전율을 높이거나두께를 줄이거나 면적을 늘리거나하지만 두께를 줄이면 누설전류가 늘어난다.면적을 넓히는것은 3차원적으로 올리는 공정을 많이 한다.

그렇기 때문에 Bridge 같은 불량품들이 발생해서 Mesh로 잡아주는 기술도 개발되었다.

고유전율 유전체 적용 사례

유전상수가 커지면 에너지 밴드갭이 줄어서 누설전류 값이 늘어난다.

서로 상보적인 관계가 있기 때문에 잘 조합하는것이 중요하다.

커패시턴스와 리키지의 상관관계를 보고 개선시키고 있더라

Cb는 줄여야 하고 Cs는 늘려야 한다고 했는데

leakage currrent가 생기는데 어떻게 생기는데

어떤 경로로 생기는지 알아보도록 하자.

Junction Leakage기판과 접합 사이의 누설게이트와 드레인 사이의 누설

Off를 시켰는데 누설되는 Sub-threshold

등등 5가지의 누설 성분이 존재한다.

X축은 시간이고

시간이 지나면서 SN 전압이 낮아진다.

증폭을 시키기 위해서 감지하기 위한

전압 레벨이 있으면 최소 전압 수준이 있고

이 레벨 까지 위치를 retention time이라고 한다.

이 타임이 지나버리면 구분할 수 없다.

다시 써줄때의 시간은 REF이다.

TRET>TREF 이어야 한다.

다시 써주는 동작은 READ 동작과 똑같다.

다른점은 CSL이라는 신호가 없다.

리드 동작과 똑같지만 읽어준 데이터가 밖으로 빠져나가지는 않는다.

델타Vbl을 키워주기 위해서는 Cs를 늘려줘야한다.

2차원적인 면적을 감소시키고

3차원적인 면적을 증가시키기 위해서는

높게 쌓아올리면 된다.

메카니컬한 (넘어지거나 무너지는) 문제를 막기 위해서

Mesh 구조(실리콘 질화막 같은) 기술을 사용한다.

② 강의를 수강하고 느낀점 혹은 향후 취업 계획에 대해 정리해주세요! (200자 이상)

오늘 처음 수강하게 되었는데 따로 필기를 하지 않기 때문에 모든 워드를 받아 적으면서 공부했습니다.

반도체 소자 수업을 기존에 수강했었기 때문에 MOS나 PN 접합은 알고 있었지만

Nand Flash나 SRAM DRAM등의 구조나 동작 원리는 알지 못했습니다.

정성적으로나 정량적으로 잘 설명해주어 처음 배움에도 쉽게 받아들일 수 있었습니다.앞으로 반도체 공학을 수강하고 반도체 공정 쪽으로 연구하고 있기 때문에 취업이나 연구에많은 도움이 될것 같습니다.

[출처] ✨ 엔지닉 반도체 NCS 반도체 합격케어 학습인증 미션 작성 방법 (엔지닉&위포트│이공계/문과취업,자기소개서,NCS,GSAT,면접) | 작성자 엔지닉 공식계정

엔지닉&위포트│이공계/문과취업,자기소... : 네이버 카페

이공계/문과취업강의,인강,컨설팅,자소서,인적성,면접,NCS,GSAT,기업분석,대기업,공기업,삼성,현대

cafe.naver.com

'반도체 이야기' 카테고리의 다른 글

| [페르미 준위] 간단하게 설명하기 (1) | 2022.01.24 |

|---|---|

| 반도체 8대 공정 [1-5] (0) | 2021.02.21 |

| 반도체 8대 공정 [1-4] (0) | 2021.02.18 |

| 반도체 8대 공정 [1-3] (0) | 2021.02.17 |

| 반도체 8대 공정 [1-2] (0) | 2021.02.16 |