MOSFET의 세 가지 상태(Accumulation, Depletion, Inversion)

mos의 구조

mos의 구조

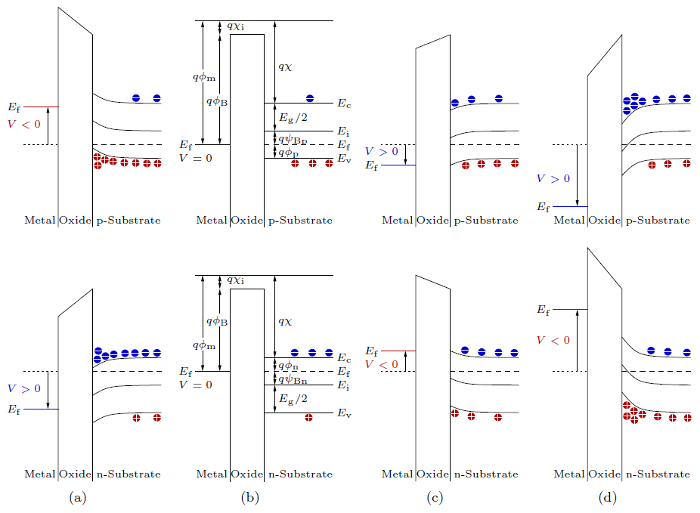

Vg(gate Voltage)에 의해서 MOSFET은 세 가지의 상태로 나뉘게 된다.

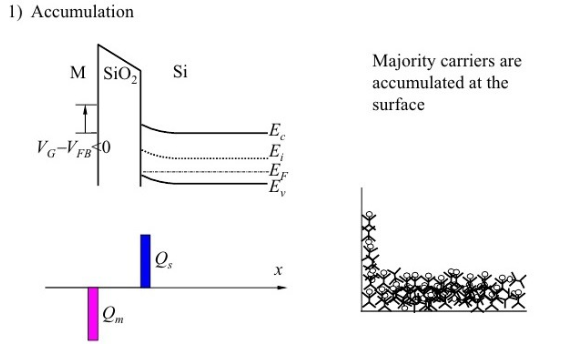

Accumulation

Metal의 에너지 다이어그램은 올라가고 실리콘의 에너지 다이어그램은 내려갑니다.

위 실리콘 에너지 다이어그램을 보면 P타입 실리콘인 것을 알 수 있습니다.

그런데 축적 상태가 되니 페르미 레벨이 Ev에 더 가까워져

도핑 농도가 높아진 것 을 볼 수 있습니다.

Qm과 Qs는 메탈과 실리콘에 쌓여있는 전하라고 생각하면 됩니다.

도핑 농도가 높아져서 P타입 실리콘에 +전하가 쌓이니

반대편에는 -전하가 쌓입니다.

Qs의 오른쪽에는 왜 전하가 없다고 돼 있을까요?

이 것은 홀이 있으면 홀을 공급해주는 Acceptor가 홀을 내어놓고 -가 됩니다.

그렇기 때문에 전하량은 0이 됩니다.

전하량과 캐리어의 개수는 다른 것입니다.(charge neutrality)

Depletion

메탈의 밴드는 내려가고 실리콘의 밴드는 올라갑니다.

페르미 레벨을 보면 Ev와 멀어져 도핑 농도가 떨어졌습니다.

Nuetral을 유지하던 Flat band에서 도핑 농도가 줄어든 것은 홀을 인위적으로 뺀 것과 같습니다.

Nuetral에서는 Acceptor가 홀, -이온으로 공존하는 영역인데 홀이 줄어들면 -이온만 남습니다.

그렇기 때문에 위를 보면 -전하가 실리콘 표면에 있고

+전하는 메탈의 표면에 있는 것을 확인할 수 있습니다.

참고! 앞에서 설명했듯이 밴드에 기울기가 있으면 전하가 있는 것입니다.

중요! 캐리어는 전압에 의해서 움직이지만 이온은 전압에 의해서 움직이지 않습니다.

그렇기 때문에 위 Depletion 상태에 있는

전하는 Space charge라고 불리는 공간을 차지하는 전하가 됩니다.

이 공간은 공핍 영역이라고 부르기도 합니다.

Inversion

실리콘의 에너지 밴드가 계속해서 올라가고

급기야 페르미 레벨이 Ev를 떠나 Ec와 가까워져

도핑의 상태가 마치 반전되는 상황이 생깁니다.

이를 Inversion 영역이라고 부르며

MOSFET의 실리콘 바디에 채널이 생기는 원리 이기도 합니다.

Weak Inversion

Weak Inversion은 MOS의 표면에 있는 Ef 페르미 레벨이

Ec와 Ev 중 Ec에 약간 더 가까운 상태입니다.

이는 MOSFET이 동작을 하는 상태는 아닙니다. 채널로 사용하기에는

Acceptor의 이온보다 일렉트론이 적은 것이죠.

Acceptor 이온의 양은 원래 이 실리콘 반도체에 있는 홀의 양과 같습니다.

그렇기 때문에 홀의 양과 같은 양의 일렉트론이 만들어지면 채널이 충분히 만들어진 것입니다.

그리고 이 상태를 Strong Inversion이라고 부릅니다.

Strong Inversion

처음에는 Acceptor이온이 100개 홀이 100개 있는 Nuetral 상태였습니다.

이 상태에서 전압을 인가하다 보니 페르미 레벨이 Ev를 떠나 Ec와 가까워지면서

Acceptor이온은 100개가 계속 유지되지만 홀 70개,

일렉트론 30개와 같이 캐리어가 반전되고 있었습니다.

홀의 개수가 일렉트론보다 작아지면 반전이 발생된 Weak Inversion입니다.

하지만 여전히 Acceptor이온은 100개입니다.

일렉트론이 100개가 되는 순간 홀은 거의 없어지고

Strong Inversion이 되어 MOS가 동작할 수 있습니다.

이때 필요한 전압이 바로 Threshold Voltage 문턱 전압이 됩니다.

이 전압은 처음 만들어진 실리콘의 도핑 농도와 관계있으며

Ef와 Ei의 포텐셜 차이의 2배 이상이 필요합니다.

추가 설명

Fig 1. 을 다시 보시면 아래의 semiconductor는 세 부분으로 나누어져 있습니다.

Source, Drain 아래는 n+, 가운데 부분은 p라고 적혀 있는 것을 보실 수 있을 것입니다.

source와 drain 전극 아래는 n type으로 강하게 도핑이 되어 있다는 뜻이고, 가운데 body라고 부르는 부분은 p type을 갖고 있는 것입니다.

즉, n-p-n의 접합을 갖고 있습니다. 이 것은 pn junction 때도 이야기했지만 기본적으로 전류가 흐르기 힘든 구조입니다. (pn 접합이 양쪽으로 반대 방향으로 있기 때문에 diode 두 개를 거꾸로 붙여 두었다고 이해하시면 편할 것 같습니다.)

즉, Fig 1과 같은 상태가 전류가 흐르지 않는 OFF 상태라고 생각하시면 됩니다.

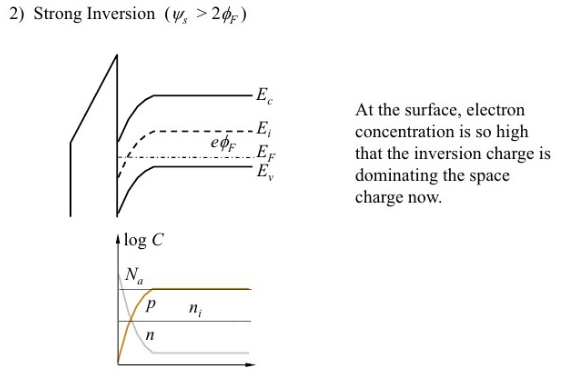

이제 다시 Fig 3을 보겠습니다.

V_G는 Gate에 가해주고 있는 voltage, V_FB는 metal electrode의 work function과 semiconductor의 work function 차이로 인해 fermi level alignment가 일어나면서 휘어졌던 band가 다시 Flat 하게 되기 위해 필요한 Gate 전압인 Flat band voltage입니다. V_T는 threshold voltage로서 channel이 생성되는 Gate 전압입니다.

현재 Fig 3의 body는 p-type입니다. 즉, hole(+)가 major carrier 인 semiconductor인 것입니다.

이때 Gate에 -를 걸어주면 가만히 있어도 hole이 더 쉽게 나올 수 있는 p-type인 반도체는 hole이 oxide와 경계 쪽에(gate와 가장 가까운 부분이기 때문) 더 쌓이게(accumulate) 됩니다. 이때가 바로 accumulation입니다. 이 때 source와 drain은 전자가 많은 n+이기 때문에 p+가 된 channel과 더 강한 depletion barrier가 형성되게 되므로 전류가 흐를 수 없습니다.(Fig 3의 가장 왼쪽)

그럼 Gate에 +를 적당히 걸어주면 어떻게 될까요?

+를 너무 세게 걸지 않고 적당히 걸어주면 oxide와 semiconductor 사이에 있던 hole은 Gate에 걸어주었던 +에 의해 밀려나게 됩니다. 제가 이전 포스팅에서도 여러 번 설명했지만, 기본적으로 semiconductor는 electron이나 hole 이 쉽게 생성될 뿐, 전기적으로 중성인 물질입니다. 이때, hole이 gate에 의해서 밀려나버리면 그 부분이 전기적으로 -를 갖게 되면서 움직일 수 있는 carrier가 급격하게 줄어들게(deplete) 됩니다. 이때가 바로 depletion입니다.역시 흐를 수 있는 carrier가 deplete 되어 버렸기 때문에 OFF 상태입니다. (Fig 3의 가운데)

그렇다면 아예 +를 엄청 세게 걸어주면 어떻게 될까요?

p-type semiconductor는 hole을 "쉽게" 내놓을 뿐, electron을 내놓지 못하는 것이 아닙니다. gate에 +를 어떤 조건 이상으로 강하게 걸어주면 (V_G > V_T) p-type에서도 electron이 풀려 나와서 oxide와 경계 부분에 쌓이게 됩니다. 이때, 계속해서 electron들이 쌓이면 어느 순간 p-type의 major carrier인 hole보다 electron이 더 많아지는, 즉 carrier 숫자가 뒤바뀌어 버리는 (inversion) 현상이 생기게 됩니다. 이제 oxide와 semiconductor의 경계 부분은 inversion 되어버린 영역인 inversion layer가 형성되어 버렸고, 이 부분은 n이 되어 버렸습니다. 그럼 이제 source, drain 도 n, 이 부분의 가운데 있던 inversion layer도 n이 되어버려 전류가 흐를 수 있는 상태가 됩니다. 이렇게 생긴 inversion layer가 바로 전류가 흐르는 channel이 되는 것이고, 이 것이 바로 transistor의 turn ON state입니다.

'반도체 이야기 > 물리전자공학&반도체소자' 카테고리의 다른 글

| 반도체소자 정리 [1] [전자 및 정공~과잉 캐리어] (0) | 2020.06.11 |

|---|---|

| pn junction minority carrier (0) | 2020.05.24 |

| MOSFET(Metal Oxide Semiconductor Field Effect Transistor)의 동작원리 (0) | 2020.04.12 |

| 반도체와 p-n 접합(p-n junction) / Ohmic contact & Schottky contact (1) | 2020.04.12 |

| 반도체소자를 위한 물리전자공학 요약 (0) | 2020.03.25 |